## Fundamentals of Computer Architecture

A Review Of Chapters 1 to 7

#### **OVERVIEW**

- This presentation includes:

- Introducing The Processor

- Fundamental Concepts I Data Representation

- Fundamental Concepts II Digital Electronic Circuits

- Registers

- The ALU

- Buses

- Memory

- Computer are everywhere

- Definition:

- It must take *input* of some sort;

- It must produce output of some sort;

- It must *process* the information somehow;

- It must have some sort of information store;

- It must have some way of controlling what it does.

- Most computers are embedded in other devices

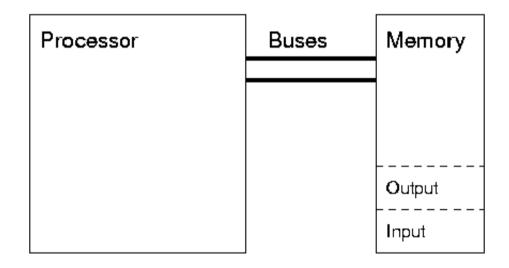

- A von Neumann architecture,

- We need:

- A processor to process information, and to control the system;

- Memory for data and instruction storage;

- Some form of input device;

Some form of output device.

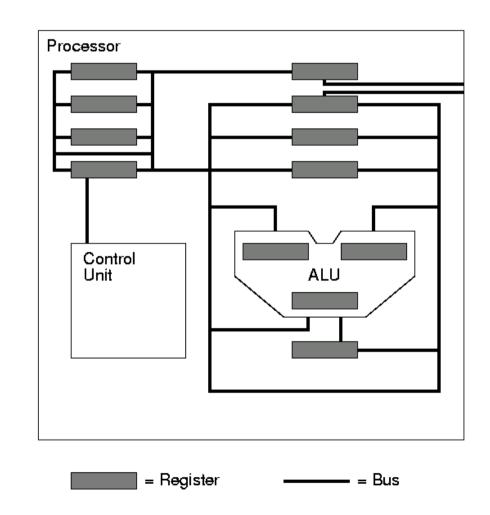

- To build our simple processor we need the following components:

- Some Registers a register is a store where we can place one piece of data;

- An Arithmetic Logic Unit, or ALU - a very basic calculator for our processor.

- A Control Unit, or CU to run the processor;

- Some buses to allow us to move data from one component to another.

#### We covered:

- Number representation decimal, binary, octal, hexadecimal and Binary Coded Decimal (BCD);

- Conversion between different bases;

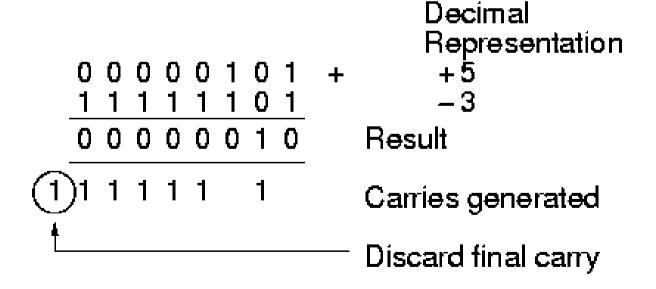

- Binary arithmetic;

- Signed representations sign and modulus, 1's complement, 2's complement and floating point;

- Logic operations AND, OR and NOT;

- Data representation ASCII and Unicode.

- The simple rule for obtaining the 2's complement representation of the negative of a number is

- Flip the bits

- Add 1

| 00000111        | Representation<br>+7 |

|-----------------|----------------------|

| 11111000        | Flip the bits        |

| 1               | Add 1                |

| 1 1 1 1 1 0 0 1 | Result represents –7 |

Decimal

Now we know how to figure out the representation of a negative number, let's try some arithmetic

|            |   |   |   |   |   |   |   | Decimal<br>Representation     |

|------------|---|---|---|---|---|---|---|-------------------------------|

| 0 1<br>0 0 | _ | - | - | _ | _ | _ | + | +88<br>+41                    |

| 1 0        | 0 | 0 | 0 | 0 | 0 | 1 |   | Initial result                |

| 1 1        | 1 | 1 |   |   |   | - |   | Carries generated             |

| 1 0        | 0 | 0 | 0 | 0 | 0 | 1 |   | Initial result is negative    |

| 0 1        | 1 | 1 | 1 | 1 | 1 | 0 |   | Flip the bits                 |

|            |   |   |   |   |   | 1 |   | Add 1                         |

| 0 1        | 1 | 1 | 1 | 1 | 1 | 1 |   | Result is therefore -127 ???? |

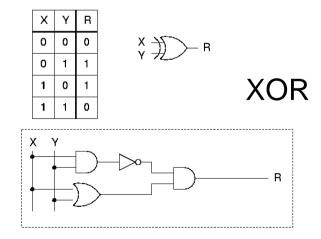

#### ASCII

- For example, the ASCII code for the letter 'R' is found as follows:

- The column that 'R' is in is labelled with the hexadecimal digit 5;

- The row that 'R' is in is labelled with the hexadecimal digit 2;

- This produces the hexadecimal value 52<sub>16</sub>.

- ASCII is being replaced by 16bit Unicode.

|                       |   | Hi         | gh F | lexa | deci | mal | Digit |   |     |

|-----------------------|---|------------|------|------|------|-----|-------|---|-----|

| `                     |   | 0          | 1    | 2    | 3    | 4   | 5     | 6 | 7   |

|                       | 0 | NUL        | DCL  |      | 0    | @   | Р     | í | р   |

|                       | 1 | SOH        | DC1  |      | 1    | Α   | Ø     | а | q   |

|                       | 2 | STX        | DC2  | =    | 2    | В   | R     | b | r   |

| Ξ                     | 3 | ETX        | DСЗ  | #    | 3    | С   | S     | С | s   |

| ă                     | 4 | EOT        | DC4  | \$   | 4    | D   | Т     | d | t   |

| nal                   | 5 | ENQ        | NAK  | %    | 5    | E   | U     | Ð | u   |

| Low Hexadecimal Digit | 6 | ACK        | SYN  | &    | 6    | F   | ٧     | f | ٧   |

| ad                    | 7 | BEL        | ЕТВ  | ,    | 7    | G   | W     | g | w   |

| ě                     | 8 | BS         | CAN  | (    | 8    | Ι   | Χ     | h | х   |

| ₹                     | 9 | нт         | EM   | )    | 9    | I   | Υ     | Í | у   |

| ت                     | Α | LF         | SUB  | *    | :    | J   | Z     | j | z   |

|                       | В | <b>V</b> T | ESC  | +    | ;    | K   | [     | k | {   |

|                       | С | FF         | FS   | ,    | <    | L   | 1     |   |     |

|                       | D | CR         | GS   | _    | =    | М   | ]     | m | }   |

|                       | E | so         | RS   |      | >    | N   | ٨     | n | 2   |

|                       | F | SI         | US   | 1    | ?    | 0   | _     | 0 | DEL |

- We covered:

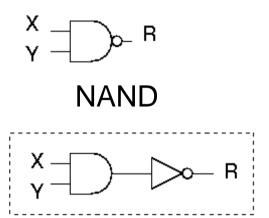

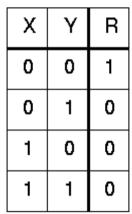

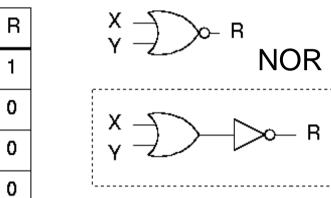

- Gate logic AND, OR and NOT;

- How to build circuits with gates;

- Modelling circuits with truth tables;

- Boolean algebra, including De Morgan's laws.

| Х | Υ | R |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| Х | Υ | R |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

$$Y \longrightarrow R$$

| Х | Υ | R |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

| Х | Υ | Ø | O |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

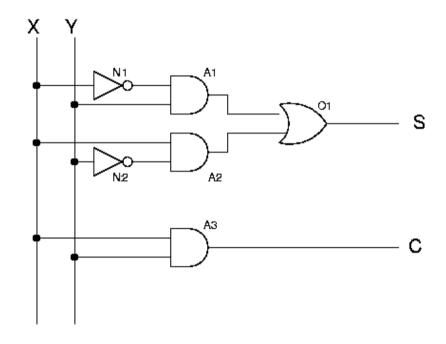

A circuit diagram can be derived from a truth table

- Boolean Algebra

- The set of rules that we can make use of are known as the identities of boolean algebra.

- Each identity (apart from the absorbtion and double complement) has two forms, one for the AND form, and the other for the OR form.

| Law              | Identity                                     |

|------------------|----------------------------------------------|

| Absorbtion       | $x \cdot (x+y) = x$                          |

| Associative      | x + (y+z) = (x+y) + z                        |

|                  | $x \cdot (y \cdot z) = (x \cdot y) \cdot z$  |

| Complement       | $x + \bar{x} = 1$                            |

|                  | $x \cdot \bar{x} = 0$                        |

| Commutative      | x + y = y + x                                |

|                  | $x \cdot y = y \cdot x$                      |

| De Morgan's Laws | $\overline{(x \cdot y)} = \bar{x} + \bar{y}$ |

|                  | $\overline{(x+y)} = \bar{x} \cdot \bar{y}$   |

| Distributive     | $x + (y \cdot z) = (x + y) \cdot (x + z)$    |

|                  | $x \cdot (y+z) = (x \cdot y) + (x \cdot z)$  |

| Dominance        | x + 1 = 1                                    |

|                  | $x \cdot 0 = 0$                              |

| Double           | $\overline{(\bar{x})} = x$                   |

| Complement       | ,                                            |

| Idempotent       | x + x = x                                    |

|                  | $x \cdot x = x$                              |

| Identity         | x + 0 = x                                    |

|                  | $x \cdot 1 = x$                              |

#### Boolean Algrebra

De Morgan's Laws can help us in the creation of efficient digital circuits.

$$\frac{\overline{(x \cdot y)} = \bar{x} + \bar{y}}{(x + y)} = \bar{x} \cdot \bar{y}$$

| Gate | Number of transistors |

|------|-----------------------|

| AND  | 3                     |

| OR   | 3                     |

| NOT  | 1                     |

| NAND | 2                     |

| NOR  | 2                     |

- We covered:

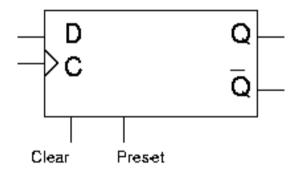

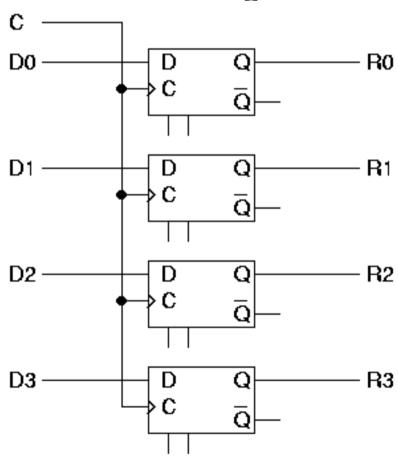

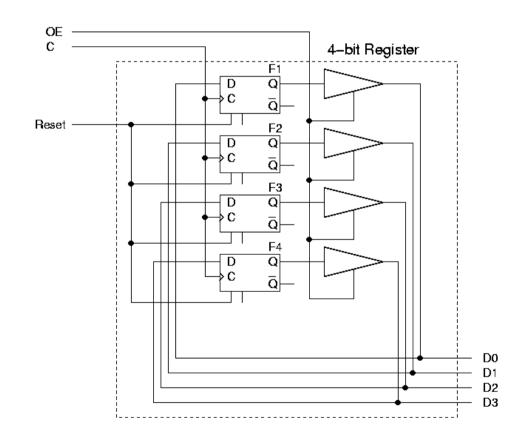

- Bistables the RS latch, the D latch and the D flipflop;

- How to build a register;

- Tri-state logic;

- The concept of a clock and a clock cycle.

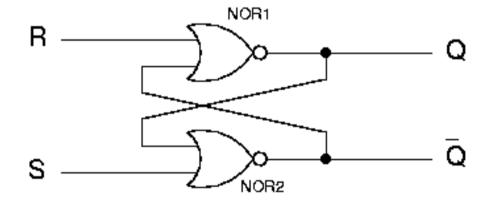

#### The RS Latch

| R | S | Description                   |

|---|---|-------------------------------|

| 0 | 0 | Q is left at what it was pre- |

|   |   | viously set to                |

| 0 | 1 | Q = 1                         |

| 1 | 0 | Q = 0                         |

| 1 | 1 | $Q = \bar{Q} = 0$             |

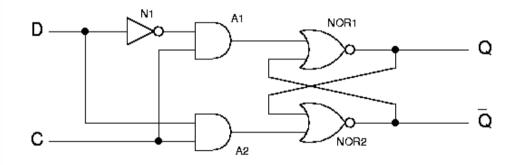

#### The D Latch

| D | С | Description                   |

|---|---|-------------------------------|

| 0 | 0 | Q is left at what it was pre- |

|   |   | viously set to.               |

| 0 | 1 | Q = 0                         |

| 1 | 0 | Q is left at what it was pre- |

|   |   | viously set to.               |

| 1 | 1 | Q = 1                         |

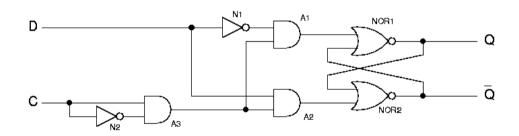

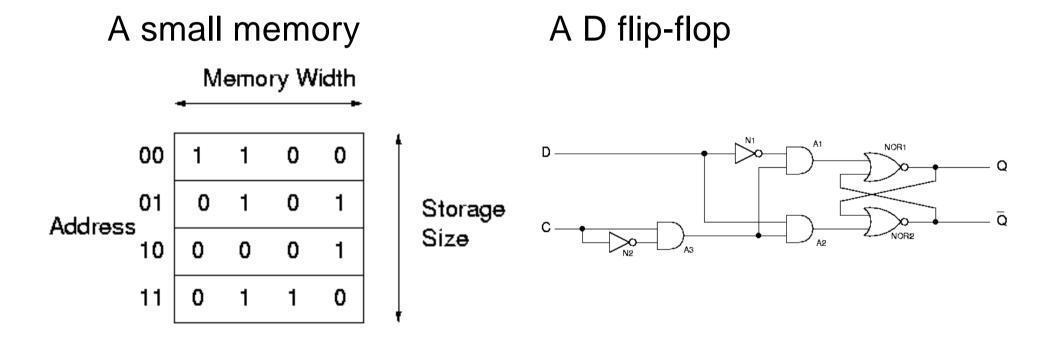

#### The D Flip-flop

A 4-bit register

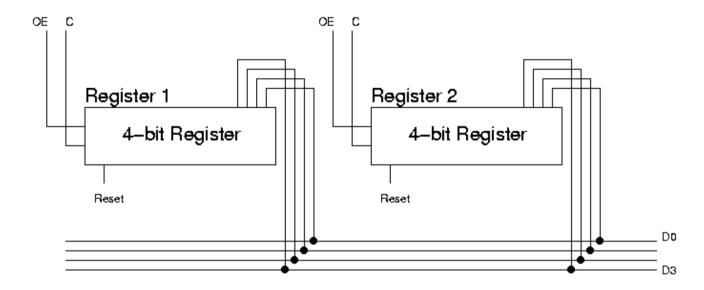

A 4-bit register attached to a bus

- To move a bit pattern from register 1 to register 2 we would do as before:

- Set register 1 OE to 1 (bit pattern now on the bus);

- Clock register 2 (for register 2 to take the bit pattern from the bus);

- Set register 1 OE to 0;

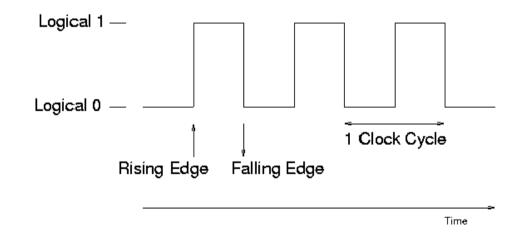

- The Clock cycle

- There are effectively four different types of trigger. These are:

- 1 triggered when the clock signal becomes 1;

- 0 triggered when the clock signal becomes 0;

- Positive edge triggered when the clock signal changes from a 0 to a 1;

- Negative edge triggered when the clock signal changes from a 1 to a 0.

#### We covered:

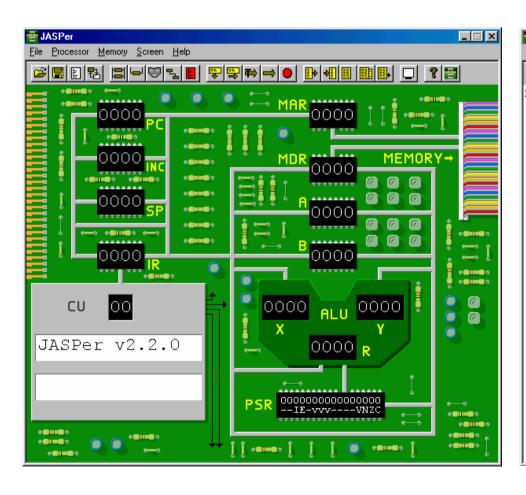

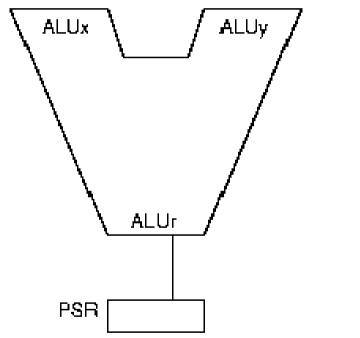

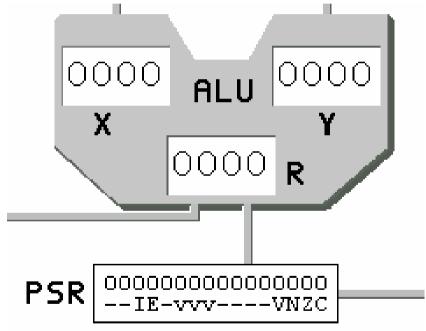

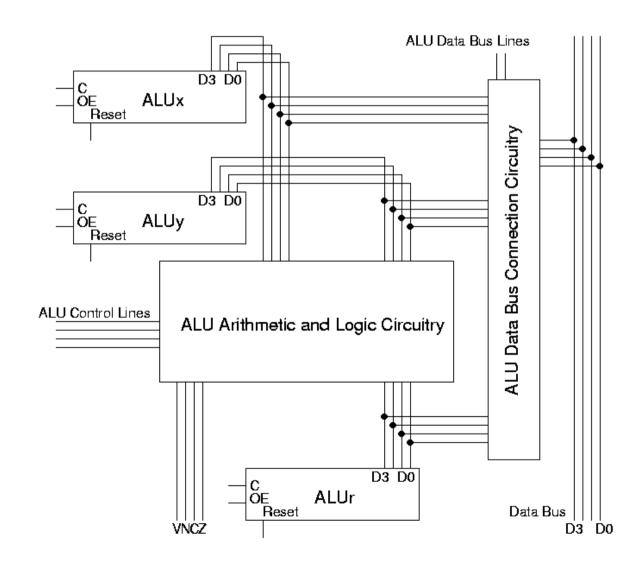

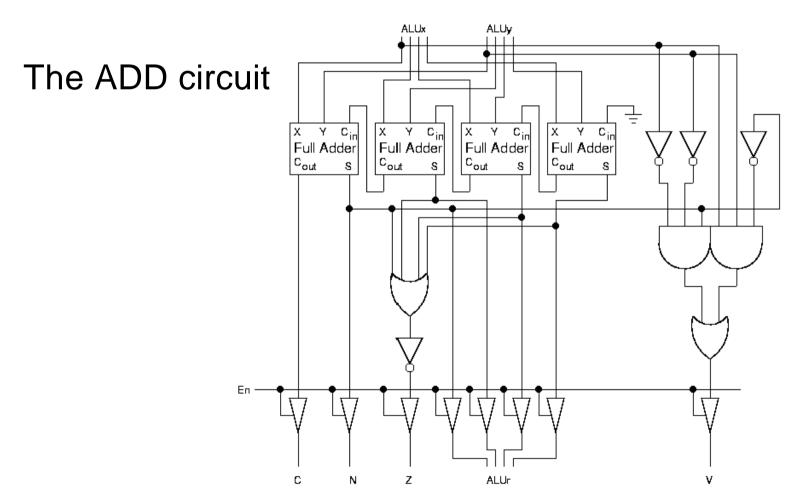

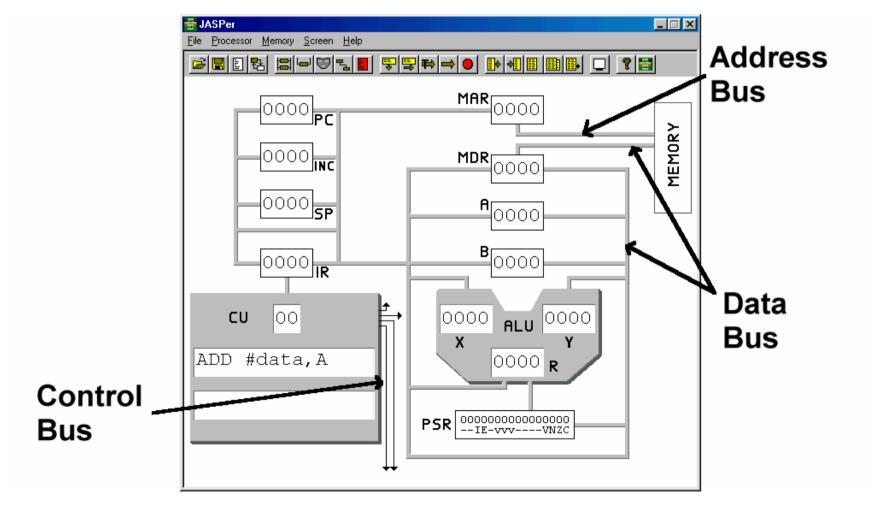

- The role of the ALU and PSR within the processor;

- The control circuitry of the ALU;

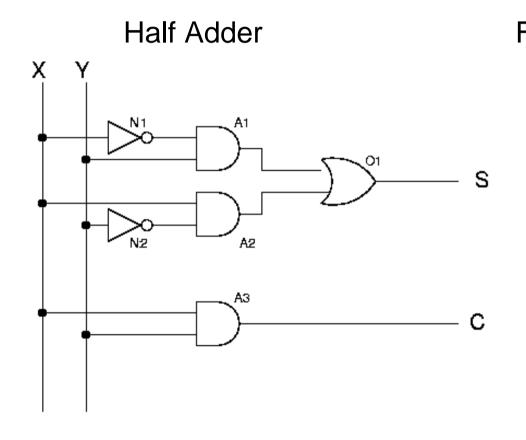

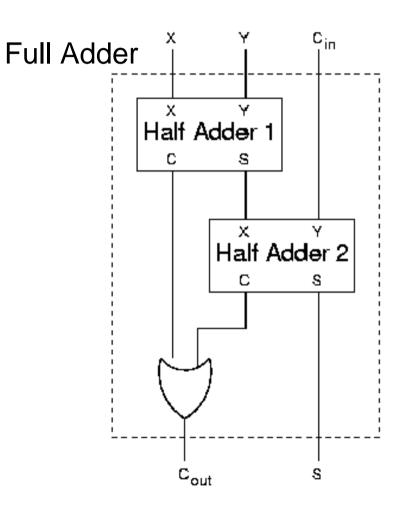

- Adder circuits the half adder and the full adder;

- Building circuits to demonstrate the functionality of the ALU – the ADD, SL and NEG circuits.

#### **Buses**

- We covered:

- Processor buses the data bus, the address bus and the control bus;

- Building a bus with gate logic;

- Timing diagrams.

#### Buses

### **Buses**

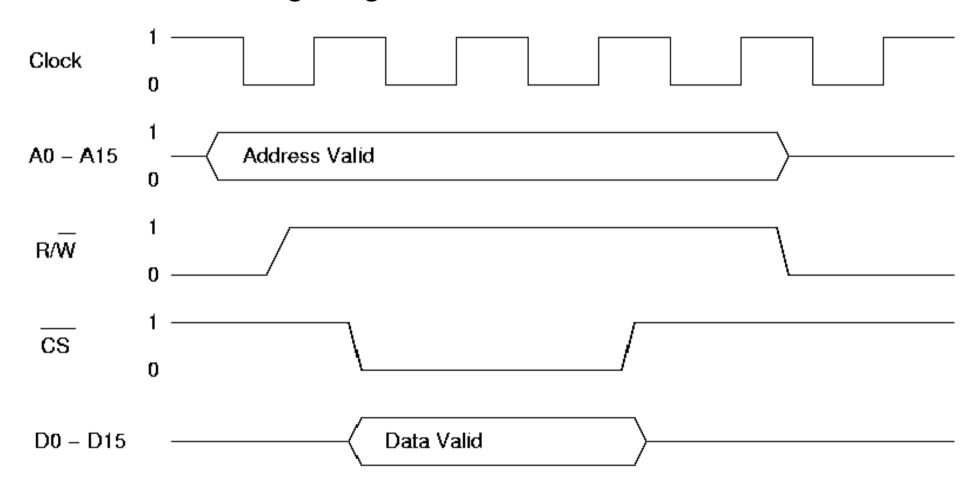

#### A timing diagram

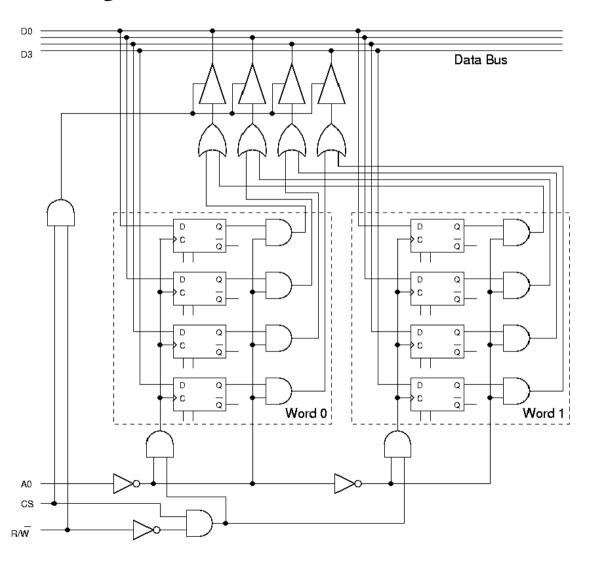

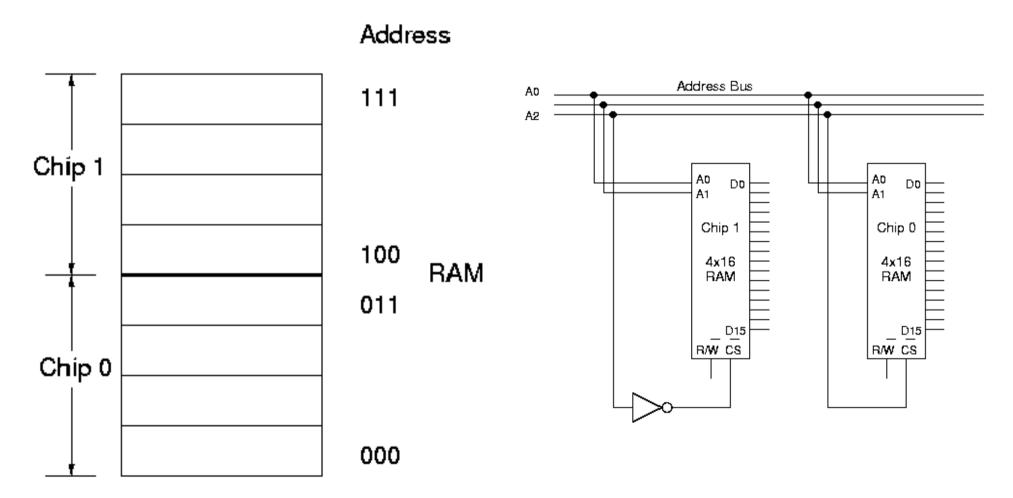

- We covered:

- The concepts of memory;

- How to build memory from gate logic;

- Types of memory;

- Address decoding strategies;

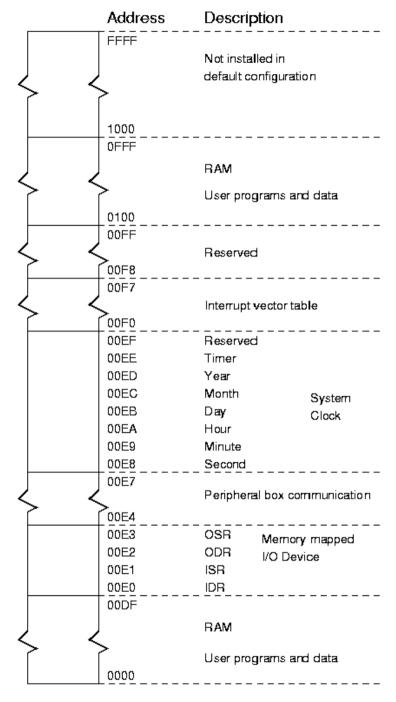

- Memory maps.

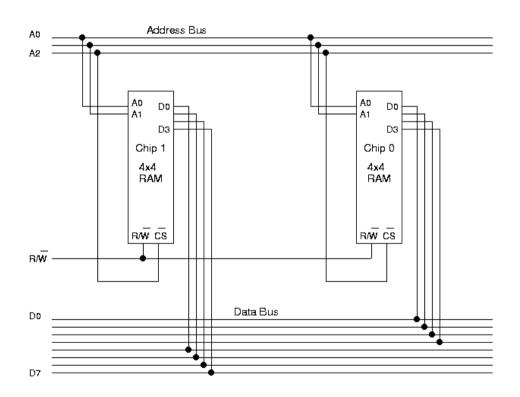

#### Building wider memories

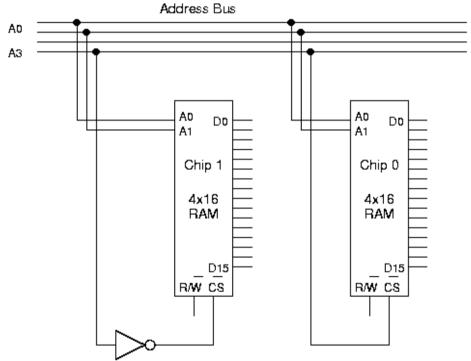

#### Partial address mapping

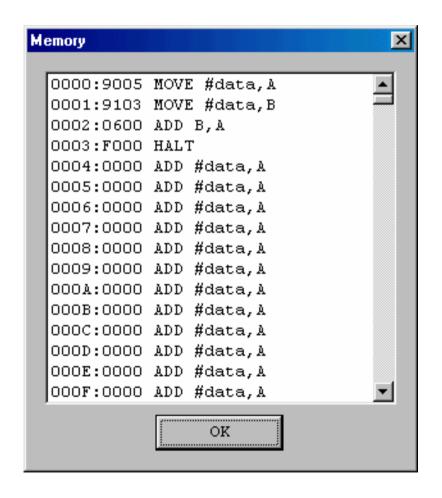

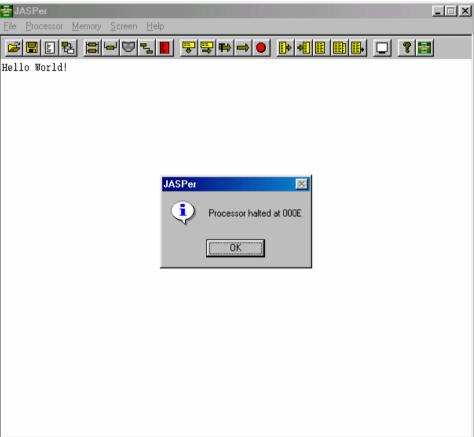

#### JASPer memory